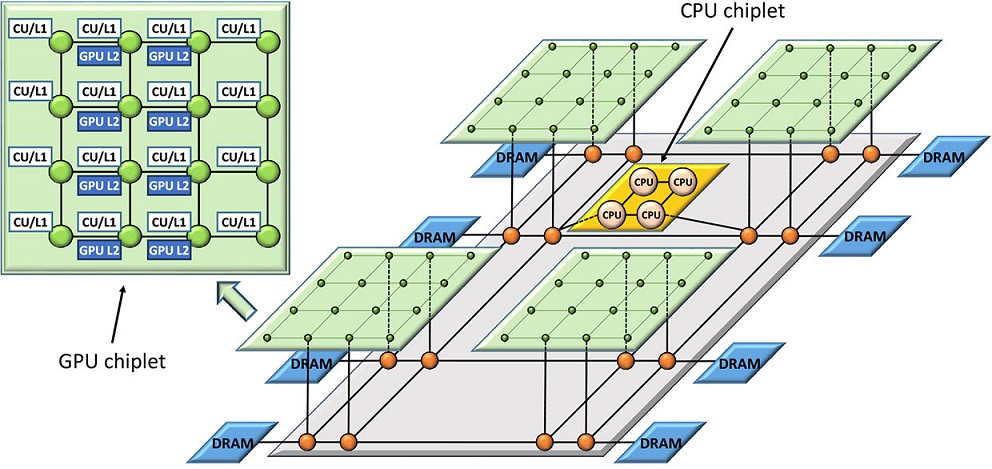

AMD prévoit son retour dans la danse des processeurs à haute performance de longue date, avec par exemple son Infinity Fabric pour relier différentes puces dans un même boîtier (un processeur principal et une carte graphique, notamment). Il semblerait que le fabricant envisage de pousser cette technologie un cran plus loin avec des pucettes (chiplets), cest-à-dire de très petites puces que lon assemblerait dans un même boîtier pour former un processeur complet. Chacune de ces pucettes serait bien plus petite et moins chère à fabriquer (on pourrait en faire des milliers sur une même galette de silicium, plutôt que quelques dizaines à centaines de processeurs complets sur la même surface). Le boîtier interfaçant toutes ces pucettes pourrait être bien plus grand quaujourdhui, en intégrant plus de fonctionnalités encore : outre les curs de calcul, on pourrait compter la mémoire ou lentièreté de lélectronique de puissance. Ces petits composants communiqueraient alors ensemble à laide dun interposeur, une forme de réseau interne au boîtier. Lidée nest pas exclusive à AMD : elle se retrouve à la base de certains processeurs Xeon Scalable, où une version épurée du mécanisme est utilisée pour inclure un FPGA, par exemple.

AMD prévoit son retour dans la danse des processeurs à haute performance de longue date, avec par exemple son Infinity Fabric pour relier différentes puces dans un même boîtier (un processeur principal et une carte graphique, notamment). Il semblerait que le fabricant envisage de pousser cette technologie un cran plus loin avec des pucettes (chiplets), cest-à-dire de très petites puces que lon assemblerait dans un même boîtier pour former un processeur complet. Chacune de ces pucettes serait bien plus petite et moins chère à fabriquer (on pourrait en faire des milliers sur une même galette de silicium, plutôt que quelques dizaines à centaines de processeurs complets sur la même surface). Le boîtier interfaçant toutes ces pucettes pourrait être bien plus grand quaujourdhui, en intégrant plus de fonctionnalités encore : outre les curs de calcul, on pourrait compter la mémoire ou lentièreté de lélectronique de puissance. Ces petits composants communiqueraient alors ensemble à laide dun interposeur, une forme de réseau interne au boîtier. Lidée nest pas exclusive à AMD : elle se retrouve à la base de certains processeurs Xeon Scalable, où une version épurée du mécanisme est utilisée pour inclure un FPGA, par exemple.

Néanmoins, cette décomposition des processeurs nest pas sans poser de problème. En effet, avec un réseau très simple, si les pucettes ne sont pas bien conçues, lutilisateur court le risque davoir des embouteillages, voire une étreinte fatale : par exemple, si les pucettes tentent de communiquer en cercle, il est possible que toutes attendent pour la suivante et que donc rien ne se passe. La difficulté vient que, dans une architecture à base de pucettes, il est impossible de prévoir tous les chemins qui seront possibles à lintérieur du boîtier, donc toutes les situations potentiellement dangereuses pour le système au complet. Si lon se met à concevoir toutes les pucettes simultanément en prenant en compte ces possibilités, on casse lavantage même de cette approche : les pucettes ne seraient absolument plus indépendantes et ne pourraient plus être mélangées arbitrairement.

AMD a récemment décrit sa solution pour éviter ce genre dinconvénients. Ses ingénieurs ont trouvé un ensemble de règles assez simples qui garantissent quil ny ait jamais détreinte fatale, en restreignant les endroits où les données peuvent entrer et sortir, ainsi que leur direction. Ainsi, peu importe la composition des pucettes, on peut prouver que le boîtier ne connaîtra jamais de problème ; on peut concevoir une de ces pucettes en considérant que le reste du boîtier nest quune seule autre pucette.

Plus de détails ? Voir larticle Modular Routing Design for Chiplet-based Systems (à paraître).

Source et images : AMD Tackles Coming Chiplet Revolution With New Chip Network Scheme.

Vous avez lu gratuitement 1 356 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.