Les besoins en mémoire des serveurs actuels ne cessent daugmenter : pour traiter des volumes de données de plus en plus grands, pour gérer de plus en plus de machines virtuelles, les technologies actuelles montrent leurs limites. Par exemple, certains serveurs peuvent gérer jusquà un téraoctet et demi de mémoire

mais cela ne suffira probablement plus dans quelques années.

Les besoins en mémoire des serveurs actuels ne cessent daugmenter : pour traiter des volumes de données de plus en plus grands, pour gérer de plus en plus de machines virtuelles, les technologies actuelles montrent leurs limites. Par exemple, certains serveurs peuvent gérer jusquà un téraoctet et demi de mémoire

mais cela ne suffira probablement plus dans quelques années.En effet, chaque serveur na de la place que pour un nombre limité de barrettes (chacune étant constituée dun certain nombre de puces). De plus, les processeurs ne peuvent pas offrir des canaux pour connecter ces barrettes en quantité infinie : les contrôleurs de mémoire étendent leurs capacités pour gérer plusieurs barrettes par canal, ce qui ne peut pas non plus se faire à linfini. Pour continuer à monter en capacité, pas dautre choix : il faut que chaque barrette de mémoire ait une capacité plus grande (idéalement, sans consommer trop dénergie).

Cest pour cela que la norme actuelle, DDR4, sera à terme remplacée par DDR5. La première permet de réaliser des puces de mémoire qui montent jusque seize gigaoctets et den empiler huit (une barrette étant alors constituée de plusieurs piles). Au contraire, DDR5 permettra de monter jusquà trente-deux gigaoctets et dempiler plus de puces même si les détails ne sont pas encore connus.

DDR5 is mostly a capacity solution, more than performance. Marc Greenberg, Cadence

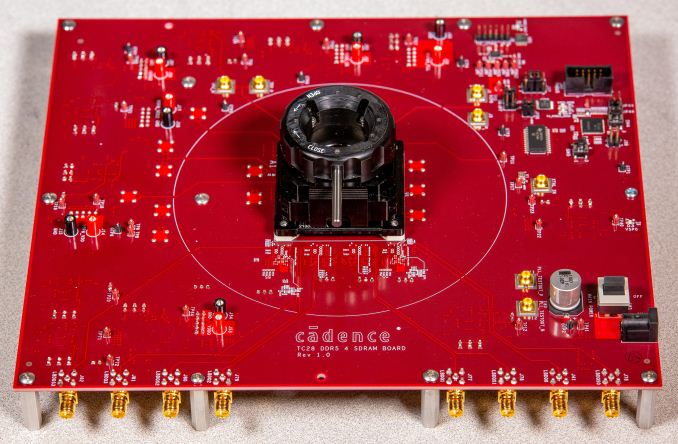

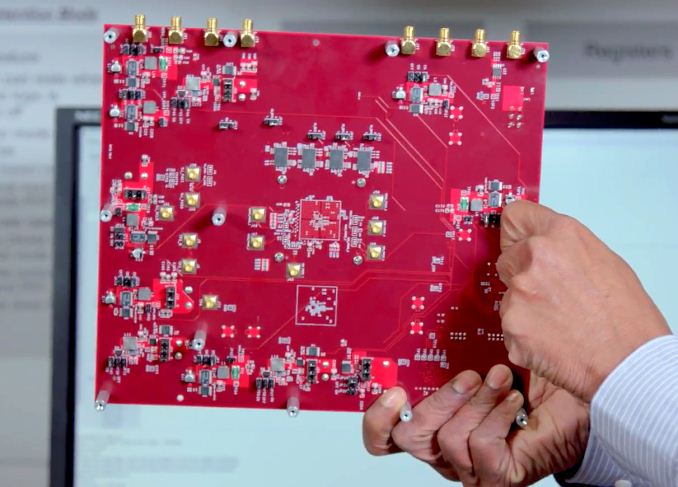

Cadence et Micron ont justement annoncé cette semaine les premières puces de mémoire (Micron) et les contrôleurs associés (Cadence) pour la version provisionnelle actuelle de la norme DDR5, utilisant le processus de fabrication en 7 nm de TSMC. La combinaison permet actuellement de monter à quatre milliards quatre cent mille transferts par seconde bien plus que la mémoire DDR4 surcadencée à lextrême. Au niveau énergétique, la tension dalimentation baisse de 1,2 V à 1,1 V. Au stade des prototypes, cette technologie permet donc de gagner sur tous les tableaux selon lorganisation de normalisation JEDEC, la version finale pourrait monter à plus de six milliards de transferts par seconde.

Les barrettes devraient garder le même nombre de broches, cest-à-dire deux cent quatre-vingt-huit, mais avec un arrangement différent pour éviter la confusion avec les barrettes DDR4. Néanmoins, des différences architecturales seront bien présentes : chaque barrette disposera de deux canaux pour échanger les données, avec une largeur de trente-deux bits chacun (une spécificité reprise à la technologie LPDDR4, une variante de DDR4 prévue pour une consommation énergétique moindre, qui dispose de deux canaux de seize bits). Chaque canal aura également ses bus de contrôle (adresse, commande, pour un total de quatorze bits).

Au vu des vitesses considérées, les barrettes haut de gamme disposeront de leur propre régulateur de tension, afin de garder une alimentation très stable. En effet, la norme autorise une variation de trois pour cent de la tension dalimentation (donc 1,1 ± 0,033 V), ce qui ne sera pas suffisant pour atteindre les plus hauts débits. On ne retrouvera probablement pas ce genre déquipement pour les barrettes destinées au grand public, les besoins en bande passante nétant bien souvent pas comparables.

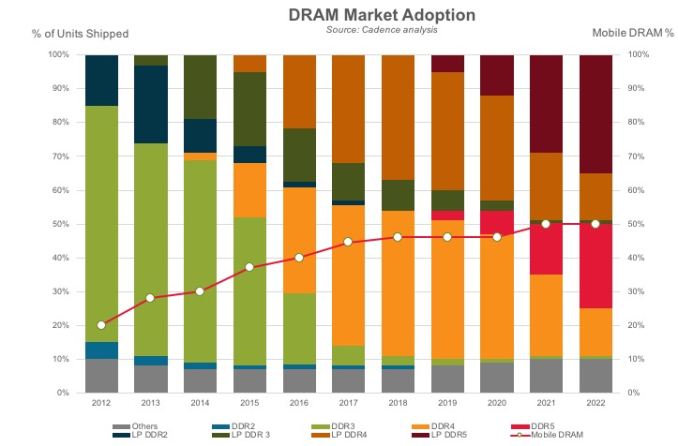

Les attentes de Cadence pour ladoption de cette nouvelle norme sont assez agressives : les premiers produits débarqueraient en 2019 (le plus probablement, des serveurs, qui utiliseraient la génération de processeurs de la fin 2019), la DDR5 dépasserait la DDR4 dici à 2022. Le passage au grand public se ferait vers 2021, avec une grande augmentation des parts de marché.

Les spécifications finales de DDR5 sont prévues pour cet été, les échantillons de tous les producteurs de mémoire pourraient arriver dans la même période.

Reste à savoir si les processeurs ne devront pas bientôt passer à cent vingt-huit bits dadresse plutôt que les soixante-quatre actuels

Source et images : Cadence and Micron Demo DDR5-4400 IMC and Memory, Due in 2019.

de mon Pentium 2 et de ces 4-5 barrettes disparates achetées sur 4 - 5 ans : des évolutions à pas chères mais qu'ils se sont fait ressentir

de mon Pentium 2 et de ces 4-5 barrettes disparates achetées sur 4 - 5 ans : des évolutions à pas chères mais qu'ils se sont fait ressentir )

)